#### **General Description**

The MAX5417/MAX5418/MAX5419 nonvolatile, linear-taper, digital potentiometers perform the function of a mechanical potentiometer by replacing the mechanics with a simple 2-wire digital interface, allowing communication with multiple devices. Each device performs the same function as a discrete potentiometer or variable resistor and has 256 tap points.

The devices feature an internal, nonvolatile EEPROM used to store the wiper position for initialization during power-up. The fast-mode I<sup>2</sup>C-compatible serial interface allows communication at data rates up to 400kbps, minimizing board space and reducing interconnection complexity in many applications. Each device is available with one of four factory-preset addresses (see the *Ordering Information/Selector Guide*) and features an address input for a total of eight unique address combinations.

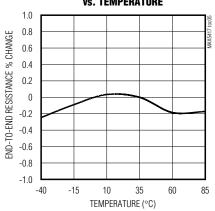

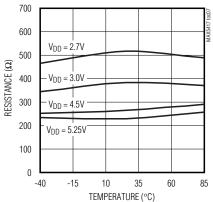

The MAX5417/MAX5418/MAX5419 provide three nominal resistance values:  $50 k\Omega$  (MAX5417),  $100 k\Omega$  (MAX5418), or  $200 k\Omega$  (MAX5419). The nominal resistor temperature coefficient is  $35 ppm/^{\circ}C$  end-to-end, and only  $5ppm/^{\circ}C$  ratiometric. This makes the devices ideal for applications requiring a low-temperature-coefficient variable resistor, such as low-drift, programmable gain-amplifier circuit configurations.

The MAX5417/MAX5418/MAX5419 are available in a 3mm x 3mm 8-pin TDFN package, and are specified over the extended -40°C to +85°C temperature range.

## **Applications**

Mechanical Potentiometer Replacement Low-Drift Programmable-Gain Amplifiers Volume Control

Liquid-Crystal Display (LCD) Contrast Control

#### **Features**

- Power-On Recall of Wiper Position from Nonvolatile Memory

- ◆ Tiny 3mm x 3mm 8-Pin TDFN Package

- ♦ 35ppm/°C End-to-End Resistance Temperature Coefficient

- ◆ 5ppm/°C Ratiometric Temperature Coefficient

- ♦ 50kΩ/100kΩ/200kΩ Resistor Values

- ♦ Fast I<sup>2</sup>C-Compatible Serial Interface

- ♦ 500nA (typ) Static Supply Current

- ♦ Single-Supply Operation: +2.7V to +5.25V

- ♦ 256 Tap Positions

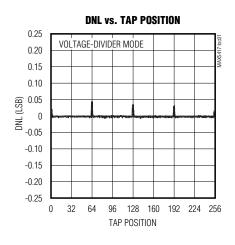

- ♦ ±0.5 LSB DNL in Voltage-Divider Mode

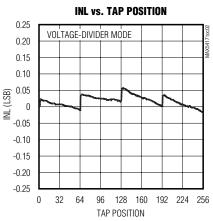

- ♦ ±0.5 LSB INL in Voltage-Divider Mode

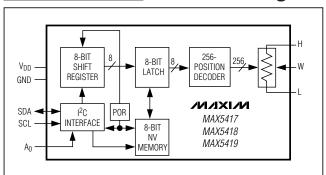

#### Functional Diagram

## **Ordering Information/Selector Guide**

| PART         | TEMP RANGE     | I <sup>2</sup> C ADDRESS | <b>R</b> ( <b>k</b> Ω) | PIN-PACKAGE | TOP MARK |

|--------------|----------------|--------------------------|------------------------|-------------|----------|

| MAX5417LETA+ | -40°C to +85°C | 010100A <sub>0</sub>     | 50                     | 8 TDFN-EP** | AIB      |

| MAX5417META+ | -40°C to +85°C | 010101A <sub>0</sub>     | 50                     | 8 TDFN-EP** | ALS      |

| MAX5417NETA+ | -40°C to +85°C | 010110A <sub>0</sub>     | 50                     | 8 TDFN-EP** | ALT      |

| MAX5417PETA+ | -40°C to +85°C | 010111A <sub>0</sub>     | 50                     | 8 TDFN-EP** | ALU      |

| MAX5418LETA+ | -40°C to +85°C | 010100A <sub>0</sub>     | 100                    | 8 TDFN-EP** | AIC      |

| MAX5418META+ | -40°C to +85°C | 010101A <sub>0</sub>     | 100                    | 8 TDFN-EP** | ALV      |

| MAX5418NETA+ | -40°C to +85°C | 010110A <sub>0</sub>     | 100                    | 8 TDFN-EP** | ALW      |

| MAX5418PETA+ | -40°C to +85°C | 010111A <sub>0</sub>     | 100                    | 8 TDFN-EP** | ALX      |

| MAX5419LETA+ | -40°C to +85°C | 010100A <sub>0</sub>     | 200                    | 8 TDFN-EP** | AID      |

| MAX5419META+ | -40°C to +85°C | 010101A <sub>0</sub>     | 200                    | 8 TDFN-EP** | ALY      |

| MAX5419NETA+ | -40°C to +85°C | 010110A <sub>0</sub>     | 200                    | 8 TDFN-EP** | ALZ      |

| MAX5419PETA+ | -40°C to +85°C | 010111A <sub>0</sub>     | 200                    | 8 TDFN-EP** | AMA      |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

Pin Configuration appears at end of data sheet.

<sup>\*\*</sup>Exposed pad.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND          | 0.3V to +6.0V |

|---------------------------------|---------------|

| All Other Pins to GND           |               |

| Maximum Continuous Current into | H, L, and W   |

| MAX5417                         | ±1.3mA        |

| MAX5418                         | ±0.6mA        |

| MAX5419                         | ±0.3mA        |

| Continuous Power Dissipation ( $T_A = +70^\circ$ | C)             |

|--------------------------------------------------|----------------|

| 8-Pin TDFN (derate 24.4mW/°C above               | +70°C)1951mW   |

| Operating Temperature Range                      | 40°C to +85°C  |

| Junction Temperature                             | +150°C         |

| Storage Temperature Range                        | 60°C to +150°C |

| Lead Temperature (soldering, 10s)                | +300°C         |

| Soldering Temperature (reflow)                   | +260°C         |

|                                                  |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(VDD = +2.7V to +5.25V, H = VDD, L = GND, TA = -40°C to +85°C, unless otherwise noted. Typical values are at VDD = +5V, TA = +25°C.)

| PARAMETER                              | SYMBOL          | CONDITIONS                             | MIN      | TYP   | MAX  | UNITS  |

|----------------------------------------|-----------------|----------------------------------------|----------|-------|------|--------|

| DC PERFORMANCE (VOLTA                  | GE-DIVIDER MO   | DDE)                                   |          |       |      | · II   |

| Resolution                             |                 |                                        | 256      |       |      | Taps   |

| Integral Nonlinearity                  | INL             | (Note 1)                               |          |       | ±0.5 | LSB    |

| Differential Nonlinearity              | DNL             | (Note 1)                               |          |       | ±0.5 | LSB    |

| End-to-End Temperature<br>Coefficient  | TCR             |                                        |          | 35    |      | ppm/°C |

| Ratiometric Temperature<br>Coefficient |                 |                                        |          | 5     |      | ppm/°C |

|                                        |                 | MAX5417_, 50Ω                          |          | -0.6  |      |        |

| Full-Scale Error                       |                 | MAX5418_, 100kΩ                        |          | -0.3  |      | LSB    |

|                                        |                 | MAX5419_, 200kΩ                        |          | -0.15 |      |        |

|                                        |                 | MAX5417_, 50kΩ                         |          | 0.6   |      |        |

| Zero-Scale Error                       |                 | MAX5418_, 100kΩ                        |          | 0.3   |      | LSB    |

|                                        |                 | MAX5419_, 200kΩ                        |          | 0.15  |      |        |

| DC PERFORMANCE (VARIA                  | BLE-RESISTOR    | MODE)                                  |          |       |      |        |

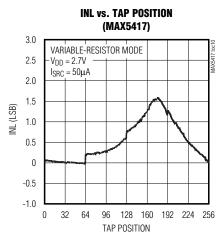

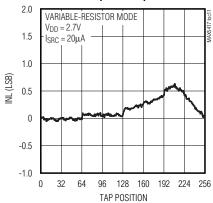

| Integral Nonlinearity                  | INL             | $V_{DD} = 3V$                          |          |       | ±3   | LSB    |

| (Note 2)                               | IINL            | $V_{DD} = 5V$                          |          |       | ±1.5 | LSD    |

|                                        |                 | $V_{DD} = 3V$ , MAX5417_, $50k\Omega$  | -1       |       | +2   |        |

| Differential Nonlinearity              | DNL             | $V_{DD} = 3V, MAX5418_{-}, 100k\Omega$ |          |       | ±1   | LOD    |

| (Note 2)                               | DINL            | $V_{DD} = 3V, MAX5419_{-}, 200k\Omega$ |          |       | ±1   | LSB    |

|                                        |                 | $V_{DD} = 5V$                          |          |       | ±1   |        |

| DC PERFORMANCE (RESIST                 | OR CHARACTE     | RISTICS)                               | <u> </u> |       |      | •      |

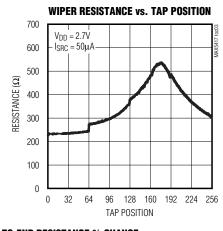

| Wiper Resistance                       | Rw              | V <sub>DD</sub> = 3V to 5.25V (Note 3) |          | 325   | 675  | Ω      |

| Wiper Capacitance                      | Cw              |                                        |          | 10    |      | рF     |

|                                        |                 | MAX5417_                               | 37.5     | 50    | 62.5 |        |

| End-to-End Resistance                  | R <sub>HL</sub> | MAX5418_                               | 75       | 100   | 125  | kΩ     |

|                                        |                 | MAX5419_                               | 150      | 200   | 250  |        |

2 \_\_\_\_\_\_*NIXI/*I

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +2.7V \text{ to } +5.25V, H = V_{DD}, L = GND, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{DD} = +5V, T_A = +25^{\circ}\text{C}.)$

| DIGITAL INPUTS                |                   |                                                                               |                       |                       |        |  |  |

|-------------------------------|-------------------|-------------------------------------------------------------------------------|-----------------------|-----------------------|--------|--|--|

| Input High Voltage (Note 4)   | \/                | V <sub>DD</sub> = 3.4V to 5.25V                                               | 2.4                   |                       | V      |  |  |

| Input High Voltage (Note 4)   | VIH               | V <sub>DD</sub> < 3.4V                                                        | 0.7 x V <sub>DD</sub> | 0.7 x V <sub>DD</sub> |        |  |  |

| Input Low Voltage             | V <sub>IL</sub>   | V <sub>DD</sub> = 2.7V to 5.25V (Note 4)                                      |                       | 0.8                   | V      |  |  |

| Low-Level Output Voltage      | Vol               | 3mA sink current                                                              |                       | 0.4                   | V      |  |  |

| Input Leakage Current         | ILEAK             |                                                                               |                       | ±1                    | μΑ     |  |  |

| Input Capacitance             |                   |                                                                               | 5                     |                       | pF     |  |  |

| DYNAMIC CHARACTERISTICS       |                   |                                                                               |                       |                       |        |  |  |

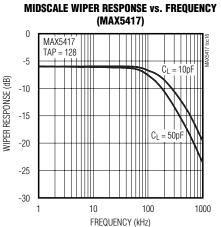

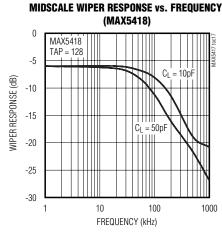

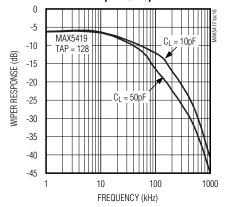

|                               |                   | MAX5417_                                                                      | 100                   |                       |        |  |  |

| Wiper -3dB Bandwidth (Note 5) |                   | MAX5418_                                                                      | 50                    |                       | kHz    |  |  |

|                               |                   | MAX5419_                                                                      | 25                    |                       |        |  |  |

| NONVOLATILE MEMORY            |                   |                                                                               |                       |                       |        |  |  |

| Data Retention                |                   | T <sub>A</sub> = +85°C                                                        | 50                    |                       | Years  |  |  |

| En di wan a a                 |                   | T <sub>A</sub> = +25°C                                                        | 200,000               |                       | Ctores |  |  |

| Endurance                     |                   | T <sub>A</sub> = +85°C                                                        | 50,000                |                       | Stores |  |  |

| POWER SUPPLY                  |                   |                                                                               |                       |                       |        |  |  |

| Power-Supply Voltage          | $V_{\mathrm{DD}}$ |                                                                               | 2.70                  | 5.25                  | V      |  |  |

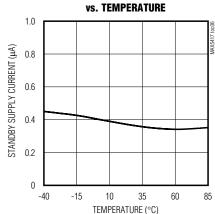

| Standby Current               | I <sub>DD</sub>   | Digital inputs = $V_{DD}$ or GND,<br>$T_A = +25$ °C                           | 0.5                   | 1                     | μΑ     |  |  |

| Programming Current           |                   | During nonvolatile write;<br>digital inputs = V <sub>DD</sub> or GND (Note 6) | 200                   | 400                   | μΑ     |  |  |

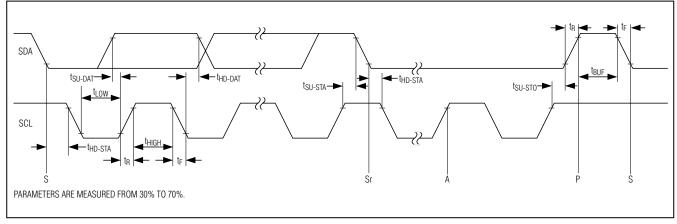

#### **TIMING CHARACTERISTICS**

$(V_{DD} = +2.7 V \text{ to } +5.25 V, H = V_{DD}, L = GND, T_{A} = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{DD} = +5 V, T_{A} = +25 ^{\circ}\text{C}$ . See Figures 1 and 2.) (Note 7)

| PARAMETER                      | SYMBOL  | CONDITIONS | MIN | TYP  | MAX | UNITS |

|--------------------------------|---------|------------|-----|------|-----|-------|

| ANALOG SECTION                 |         |            |     |      |     |       |

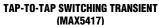

|                                |         | MAX5417_   |     | 500  |     |       |

| Wiper Settling Time (Note 8)   | tı∟     | MAX5418_   |     | 600  |     | ns    |

|                                |         | MAX5419_   |     | 1000 |     |       |

| DIGITAL SECTION                |         |            |     |      |     |       |

| SCL Clock Frequency            | fSCL    |            |     |      | 400 | kHz   |

| Setup Time for START Condition | tsu-sta |            | 0.6 |      |     | μs    |

| Hold Time for START Condition  | thd-sta |            | 0.6 |      |     | μs    |

| CLK High Time                  | tHIGH   |            | 0.6 | •    |     | μs    |

| CLK Low Time                   | tLOW    |            | 1.3 |      |     | μs    |

#### **TIMING CHARACTERISTICS (continued)**

$(V_{DD} = +2.7 \text{V to } +5.25 \text{V}, H = V_{DD}, L = GND, T_{A} = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{DD} = +5 \text{V}, T_{A} = +25 ^{\circ}\text{C}$ . See Figures 1 and 2.) (Note 7)

| PARAMETER                                      | SYMBOL           | CONDITIONS                      | MIN | TYP | MAX | UNITS |

|------------------------------------------------|------------------|---------------------------------|-----|-----|-----|-------|

| Data Setup Time                                | tsu-dat          |                                 | 100 |     |     | ns    |

| Data Hold Time                                 | thd-dat          |                                 | 0   |     | 0.9 | μs    |

| SDA, SCL Rise Time                             | t <sub>R</sub>   |                                 |     |     | 300 | ns    |

| SDA, SCL Fall Time                             | t <sub>F</sub>   |                                 |     |     | 300 | ns    |

| Setup Time for STOP Condition                  | tsu-sto          |                                 | 0.6 |     |     | μs    |

| Bus Free Time Between STOP and START Condition | t <sub>BUF</sub> | Minimum power-up rate = 0.2V/ms | 1.3 |     |     | μs    |

| Pulse Width of Spike Suppressed                | t <sub>SP</sub>  |                                 |     |     | 50  | ns    |

| Maximum Capacitive Load for Each Bus Line      | СВ               | (Note 9)                        |     | 400 |     | рF    |

| Write NV Register Busy Time                    | tBUSY            | (Note 10)                       |     |     | 12  | ms    |

- **Note 1:** The DNL and INL are measured with the potentiometer configured as a voltage-divider with H = V<sub>DD</sub> and L = GND. The wiper terminal is unloaded and measured with a high-input-impedance voltmeter.

- Note 2: The DNL and INL are measured with the potentiometer configured as a variable resistor. H is unconnected and L = GND. For the 5V condition, the wiper terminal is driven with a source current of  $80\mu$ A for the  $50k\Omega$  configuration,  $40\mu$ A for the  $100k\Omega$  configuration, and  $20\mu$ A for the  $200k\Omega$  configuration. For the 3V condition, the wiper terminal is driven with a source current of  $40\mu$ A for the  $50k\Omega$  configuration,  $20\mu$ A for the  $100k\Omega$  configuration, and  $10\mu$ A for the  $200k\Omega$  configuration.

- **Note 3:** The wiper resistance is measured using the source currents given in Note 2. For operation to V<sub>DD</sub> = 2.7V, see Wiper Resistance vs. Temperature in the *Typical Operating Characteristics*.

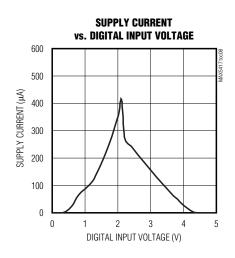

- **Note 4:** The device draws higher supply current when the digital inputs are driven with voltages between (V<sub>DD</sub> 0.5V) and (GND + 0.5V). See Supply Current vs. Digital Input Voltage in the *Typical Operating Characteristics*.

- Note 5: Wiper at midscale with a 10pF load (DC measurement). L = GND; an AC source is applied to H; and the W output is measured. A 3dB bandwidth occurs when the AC W/H value is 3dB lower than the DC W/H value.

- **Note 6:** The programming current operates only during power-up and NV writes.

- **Note 7:** SCL clock period includes rise and fall times  $t_R$  and  $t_F$ . All digital input signals are specified with  $t_R = t_F = 2$ ns and timed from a voltage level of  $(V_{IL} + V_{IH}) / 2$ .

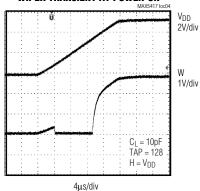

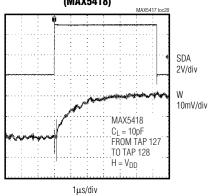

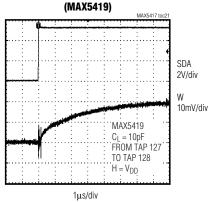

- **Note 8:** Wiper settling time is the worst-case 0% to 50% rise time measured between consecutive wiper positions. H = V<sub>DD</sub>, L = GND, and the wiper terminal is unloaded and measured with a 10pF oscilloscope probe (see the *Typical Operating Characteristics* for the tap-to-tap switching transient).

- **Note 9:** An appropriate bus pullup resistance must be selected depending on board capacitance. Refer to the document linked to this web address: www.semiconductors.philips.com/acrobat/literature/9398/39340011.pdf.

- Note 10: The idle time begins from the initiation of the stop pulse.

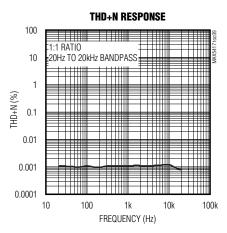

## **Typical Operating Characteristics**

$(V_{DD} = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

#### **WIPER TRANSIENT AT POWER-ON**

## STANDBY SUPPLY CURRENT

#### **WIPER RESISTANCE vs. TEMPERATURE**

## Typical Operating Characteristics (continued)

$(V_{DD} = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

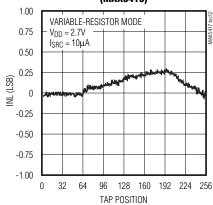

INL vs. TAP POSITION (MAX5418)

INL vs. TAP POSITION (MAX5419)

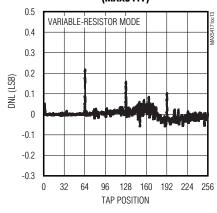

DNL vs. TAP POSITION (MAX5417)

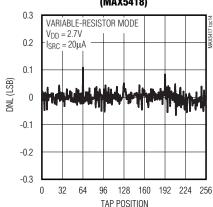

DNL vs. TAP POSITION (MAX5418)

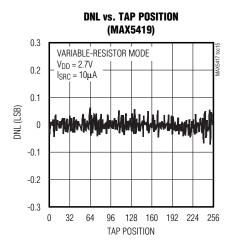

## Typical Operating Characteristics (continued)

$(V_{DD} = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

## MIDSCALE WIPER RESPONSE vs. FREQUENCY (MAX5419)

## TAP-TO-TAP SWITCHING TRANSIENT (MAX5418)

#### **Pin Description**

| PIN | NAME           | FUNCTION                                                                                                                                        |

|-----|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | $V_{DD}$       | Power-Supply Input. 2.7V to 5.25V voltage range. Bypass with a 0.1µF capacitor from V <sub>DD</sub> to GND.                                     |

| 2   | SCL            | I <sup>2</sup> C-Interface Clock Input                                                                                                          |

| 3   | SDA            | I <sup>2</sup> C-Interface Data Input                                                                                                           |

| 4   | A <sub>0</sub> | Address Input. Sets the A0 bit in the device ID address.                                                                                        |

| 5   | GND            | Ground                                                                                                                                          |

| 6   | L              | Low Terminal                                                                                                                                    |

| 7   | W              | Wiper Terminal                                                                                                                                  |

| 8   | Н              | High Terminal                                                                                                                                   |

| _   | EP             | Exposed Pad. Internally connected to GND. Connect to a large ground plane to maximize thermal performance. Not intended as an electrical point. |

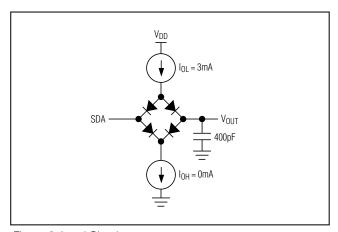

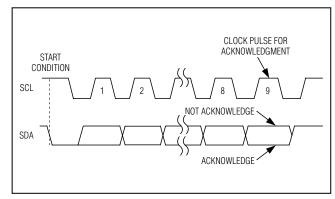

Figure 1. I<sup>2</sup>C Serial-Interface Timing Diagram

Figure 2. Load Circuit

## \_Detailed Description

The MAX5417/MAX5418/MAX5419 contain a resistor array with 255 resistive elements. The MAX5417 has a total end-to-end resistance of  $50k\Omega$ , the MAX5418 has an end-to-end resistance of  $100k\Omega$ , and the MAX5419 has an end-to-end resistance of  $200k\Omega$ . The MAX5417/MAX5418/MAX5419 allow access to the high, low, and wiper terminals for a standard voltage-divider configuration. H, L, and W can be connected in any desired configuration as long as their voltages fall between GND and VDD.

A simple 2-wire I<sup>2</sup>C-compatible serial interface moves the wiper among the 256 tap points. A nonvolatile memory stores the wiper position and recalls the stored wiper position in the nonvolatile memory upon power-up. The nonvolatile memory is guaranteed for 50 years for wiper data retention and up to 200,000 wiper store cycles.

#### **Analog Circuitry**

The MAX5417/MAX5418/MAX5419 consist of a resistor array with 255 resistive elements; 256 tap points are accessible to the wiper, W, along the resistor string between H and L. The wiper tap point is selected by programming the potentiometer through the 2-wire (I<sup>2</sup>C) interface. Eight data bits, an address byte, and a control byte program the wiper position. The H and L terminals of the MAX5417/MAX5418/MAX5419 are similar to the two end terminals of a mechanical potentiometer. The MAX5417/MAX5418/MAX5419 feature power-on reset circuitry that loads the wiper position from nonvolatile memory at power-up.

#### **Digital Interface**

The MAX5417/MAX5418/MAX5419 feature an internal, nonvolatile EEPROM that stores the wiper state for initialization during power-up. The shift register decodes the control and address bits, routing the data to the proper memory registers. Data can be written to a volatile memory register, immediately updating the wiper position, or data can be written to a nonvolatile register for storage.

The volatile register retains data as long as the device is powered. Once power is removed, the volatile register is cleared. The nonvolatile register retains data even after power is removed. Upon power-up, the power-on reset circuitry controls the transfer of data from the nonvolatile register to the volatile register.

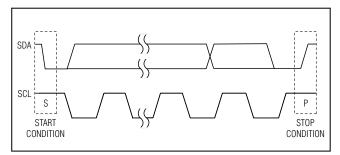

Figure 3. Start and Stop Conditions

#### Serial Addressing

The MAX5417/MAX5418/MAX5419 operate as a slave that receives data through an I<sup>2</sup>C- and SMBus<sup>™</sup>-compatible 2-wire interface. The interface uses a serial data access (SDA) line and a serial clock line (SCL) to achieve communication between master(s) and slave(s). A master, typically a microcontroller, initiates all data transfers to the MAX5417/MAX5418/MAX5419, and generates the SCL clock that synchronizes the data transfer (Figure 1).

The MAX5417/MAX5418/MAX5419 SDA line operates as both an input and an open-drain output. A pullup resistor, typically 4.7k $\Omega$ , is required on the SDA bus. The MAX5417/MAX5418/MAX5419 SCL operates only as an input. A pullup resistor, typically 4.7k $\Omega$ , is required on the SCL bus if there are multiple masters on the 2-wire interface, or if the master in a single-master system has an open-drain SCL output.

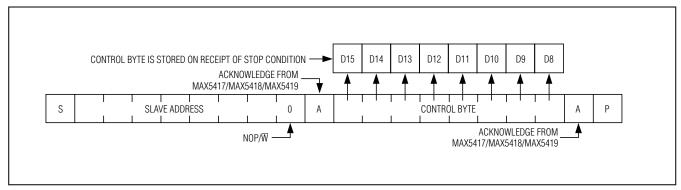

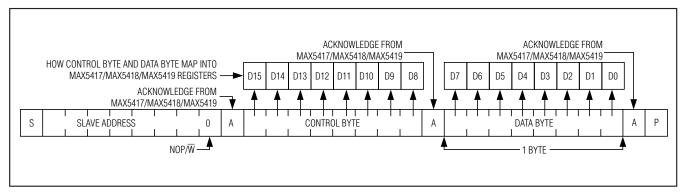

Each transmission consists of a START (S) condition (Figure 3) sent by a master, followed by the MAX5417/MAX5418/MAX5419 7-bit slave address plus the 8th bit (Figure 4), 1 command byte (Figure 7) and 1 data byte, and finally a STOP (P) condition (Figure 3).

#### Start and Stop Conditions

Both SCL and SDA remain high when the interface is not busy. A master signals the beginning of a transmission with a START condition by transitioning SDA from high to low while SCL is high. When the master has finished communicating with the slave, it issues a STOP condition by transitioning the SDA from low to high while SCL is high. The bus is then free for another transmission (Figure 3).

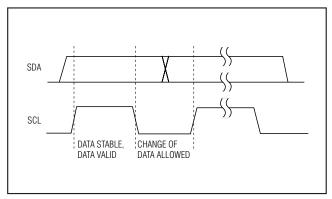

#### Bit Transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable while SCL is high (Figure 5).

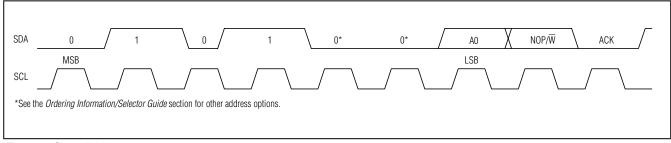

Figure 4. Slave Address

SMBus is a trademark of Intel Corporation.

Table 1. MAX5417/MAX5418/MAX5419 Address Codes

|             |            |    | Į. | ADDRESS B | YTE |    |    |       |

|-------------|------------|----|----|-----------|-----|----|----|-------|

| PART SUFFIX | A6         | A5 | A4 | А3        | A2  | A1 | A0 | NOP/W |

| L           | 0          | 1  | 0  | 1         | 0   | 0  | 0  | NOP/W |

| L           | 0          | 1  | 0  | 1         | 0   | 0  | 1  | NOP/W |

| М           | <b>M</b> 0 |    | 0  | 1         | 0   | 1  | 0  | NOP/W |

| М           | 0          | 1  | 0  | 1         | 0   | 1  | 1  | NOP/W |

| N           | 0          | 1  | 0  | 1         | 1   | 0  | 0  | NOP/W |

| N           | 0          | 1  | 0  | 1         | 1   | 0  | 1  | NOP/W |

| Р           | 0          | 1  | 0  | 1         | 1   | 1  | 0  | NOP/W |

| P           | 0          | 1  | 0  | 1         | 1   | 1  | 1  | NOP/W |

#### Acknowledge

The acknowledge bit is a clocked 9th bit that the recipient uses to handshake receipt of each byte of data (Figure 6). Thus, each byte transferred effectively requires 9 bits. The master generates the 9th clock pulse, and the recipient pulls down SDA during the acknowledge clock pulse, so the SDA line is stable low during the high period of the clock pulse. When the master transmits to the MAX5417/MAX5418/MAX5419, the devices generate the acknowledge bit because the MAX5417/MAX5418/MAX5419 are the recipients.

#### Slave Address

The MAX5417/MAX5418/MAX5419 have a 7-bit-long slave address (Figure 4). The 8th bit following the 7-bit

slave address is the NOP\overline{W} bit. Set the NOP\overline{W} bit low for a write command and high for a no-operation command.

The MAX5417/MAX5418/MAX5419 are available in one of four possible slave addresses (Table 1). The first 4 bits (MSBs) of the MAX5417/MAX5418/MAX5419 slave addresses are always 0101. The next 2 bits are factory programmed (see Table 1). Connect the A<sub>0</sub> input to either GND or V<sub>DD</sub> to toggle between two unique device addresses for a part. Each device must have a unique address to share the bus. Therefore, a maximum of eight MAX5417/MAX5418/MAX5419 devices can share the same bus.

Figure 5. Bit Transfer

Figure 6. Acknowledge

Figure 7. Command Byte Received

Figure 8. Command and Single Data Byte Received

#### Message Format for Writing

A write to the MAX5417/MAX5418/MAX5419 consists of the transmission of the device's slave address with the 8th bit set to zero, followed by at least 1 byte of information (Figure 7). The 1st byte of information is the command byte. The bytes received after the command byte are the data bytes. The 1st data byte goes into the internal register of the MAX5417/MAX5418/MAX5419 as selected by the command byte (Figure 8).

#### Command Byte

Use the command byte to select the source and destination of the wiper data (nonvolatile or volatile memory registers) and swap data between nonvolatile and volatile memory registers (see Table 2).

#### **Command Descriptions**

**VREG:** The data byte writes to the volatile memory register and the wiper position updates with the data in the volatile memory register.

**NVREG:** The data byte writes to the nonvolatile memory register. The wiper position is unchanged.

**NVREGxVREG:** Data transfers from the nonvolatile memory register to the volatile memory register (wiper position updates).

**VREGXNVREG:** Data transfers from the volatile memory register into the nonvolatile memory register.

**Table 2. Command Byte Summary**

|                     |   |    | ADDRESS BYTE |    |    |    |    |    |   |     | CONTROL BYTE |    |    |    |    |    |    |    | DATA BYTE |    |    |    |    |    |    |    |    |     |   |

|---------------------|---|----|--------------|----|----|----|----|----|---|-----|--------------|----|----|----|----|----|----|----|-----------|----|----|----|----|----|----|----|----|-----|---|

| SCL CYCLE<br>NUMBER | S | 1  | 2            | 3  | 4  | 5  | 6  | 7  | 8 | 9   | 10           | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18        | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27  | Р |

|                     |   | A6 | Α5           | A4 | АЗ | A2 | Α1 | A0 |   | ACK |              | TX | NV | V  | R3 | R2 | R1 | R0 | ACK       | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | ACK |   |

| VREG                |   | 0  | 1            | 0  | 1  | A2 | Α1 | Α0 | 0 |     | 0            | 0  | 0  | 1  | 0  | 0  | 0  | 1  |           | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |     |   |

| NVREG               |   | 0  | 1            | 0  | 1  | A2 | Α1 | Α0 | 0 |     | 0            | 0  | 1  | 0  | 0  | 0  | 0  | 1  |           | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |     |   |

| NVREGxVREG          |   | 0  | 1            | 0  | 1  | A2 | Α1 | Α0 | 0 |     | 0            | 1  | 1  | 0  | 0  | 0  | 0  | 1  |           | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Х  |     |   |

| VREGxNVREG          |   | 0  | 1            | 0  | 1  | A2 | Α1 | A0 | 0 |     | 0            | 1  | 0  | 1  | 0  | 0  | 0  | 1  |           | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Х  |     |   |

X = Don't care.

#### **Nonvolatile Memory**

The internal EEPROM consists of an 8-bit nonvolatile register that retains the value written to it before the device is powered down. The nonvolatile register is programmed with the midscale value at the factory.

#### **Power-Up**

Upon power-up, the MAX5417/MAX5418/MAX5419 load the data stored in the nonvolatile memory register into the volatile memory register, updating the wiper position with the data stored in the nonvolatile memory register. This initialization period takes 10µs.

#### Standby

The MAX5417/MAX5418/MAX5419 feature a low-power standby. When the device is not being programmed, it goes into standby mode and power consumption is typically 500nA.

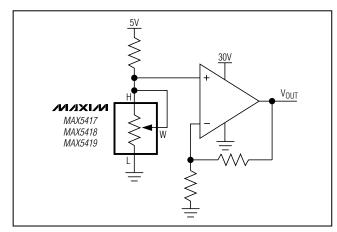

## **Applications Information**

The MAX5417/MAX5418/MAX5419 are intended for circuits requiring digitally controlled adjustable resistance, such as LCD contrast control (where voltage biasing adjusts the display contrast), or for programmable filters with adjustable gain and/or cutoff frequency.

# MAX5417 MAX5418 MAX5419 L Vout

Figure 9. Positive LCD Bias Control Using a Voltage-Divider

#### **Positive LCD Bias Control**

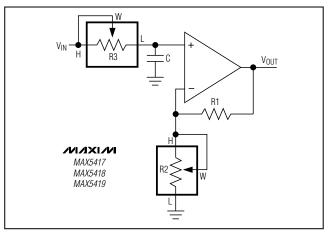

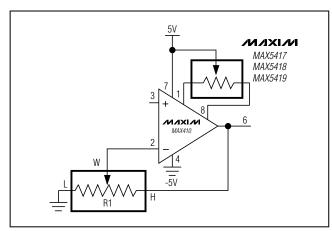

Figures 9 and 10 show an application where the voltage-divider or variable resistor is used to make an adjustable, positive LCD bias voltage. The op amp provides buffering and gain to the resistor-divider network made by the potentiometer (Figure 9) or to a fixed resistor and a variable resistor (see Figure 10).

#### **Programmable Filter**

Figure 11 shows the configuration for a 1st-order programmable filter. The gain of the filter is adjusted by R2, and the cutoff frequency is adjusted by R3. Use the following equations to calculate the gain (G) and the 3dB cutoff frequency (fc):

$$G = 1 + \frac{R1}{R2}$$

$$f_C = \frac{1}{2\pi \times R3 \times C}$$

Figure 10. Positive LCD Bias Control Using a Variable Resistor

Figure 11. Programmable Filter

Figure 13. Offset Voltage and Gain Adjustment Circuit

## Pin Configuration

Figure 12. Adjustable Voltage Reference

####

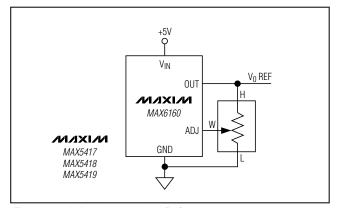

#### Adjustable Voltage Reference

Figure 12 shows the MAX5417/MAX5418/MAX5419 used as the feedback resistors in multiple adjustable voltage-reference applications. Independently adjust the output voltage of the MAX6160 from 1.23V to  $V_{\mbox{\footnotesize{IN}}}$  - 0.2V by changing the wiper positions of the MAX5417/MAX5418/MAX5419.

#### **Offset Voltage and Gain Adjustment**

Connect the high and low terminals of one potentiometer of a MAX5417 between the NULL inputs of a MAX410 and the wiper to the op amp's positive supply to nullify the offset voltage over the operating temperature range. Install the other potentiometer in the feedback path to adjust the gain of the MAX410 (see Figure 13).

#### Chip Information

PROCESS: BiCMOS

## \_Package Information

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO. |

|--------------|--------------|--------------|

| 8 TDFN-EP    | T833-1       | 21-0137      |

#### **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                                                                                                                                                                                                                                                           |             |  |  |  |

|--------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| 0                  | 2/04          | Initial release                                                                                                                                                                                                                                                                                       | _           |  |  |  |

| 1                  | 4/04          | Adding future product                                                                                                                                                                                                                                                                                 |             |  |  |  |

| 2                  | 8/04          | Adding new part                                                                                                                                                                                                                                                                                       | _           |  |  |  |

| 3                  | 3/09          | Changes to add details about exposed pad, corrections to Table 2, style edits                                                                                                                                                                                                                         | 1, 8, 12–15 |  |  |  |

| 4                  | 4/10          | Added lead-free packages to <i>Ordering Information</i> , added Soldering Temperature to <i>Absolute Maximum Ratings</i> , corrected Conditions for Differential Nonlinearity in <i>Electrical Characteristics</i> , corrected A <sub>0</sub> in <i>Pin Description</i> , corrected Figures 12 and 13 | 1, 2, 8, 13 |  |  |  |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.